Quantum Interconnects and Compilation for Distributed FTQC Architectures

September 3, 2025

About This Workshop

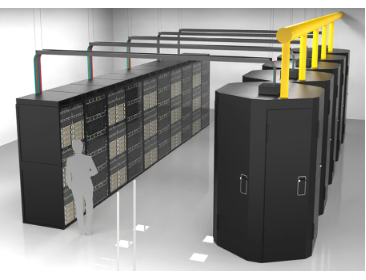

Top: Artist’s Rendition of a Distributed Quantum Supercomputer

(Image courtesy of Quantum Machines and Qolab, 2025)

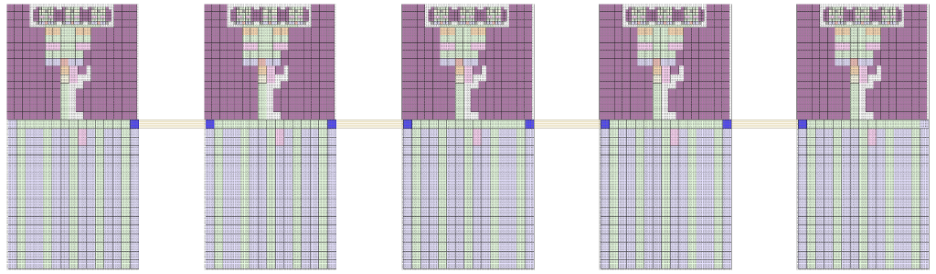

Bottom: Design Schematic of a Distributed Quantum Computing Architecture

The target audience will consist of researchers and associates from academia, industry, and government agencies interested in scaling quantum computing technologies to utility scale. While this workshop is targeted primarily at experts in building quantum devices and quantum architectures, those IEEE conference attendees with a vested interest in utility-scale quantum computing will seek to attend this workshop to learn about the latest developments and to benefit from the ability to network in this exciting field of research. We expect attendees to have working knowledge of quantum computing in general, with a focus on either experimental or theoretical aspects relevant to FTQC. While this workshop aims to be an interdisciplinary introduction to various topics, we hope to connect experts in the various fields, thus pushing the limits of current expertise. However, non-experts will be very likely to follow most discussions. Potential audience invitees may also include guests such as business investors and government representatives who are interested in near- and long-term prospects for the field of quantum computing.

Agenda

Session I |

Chair: Artur Scherer, 1QBit |

10:00 – 10:10 |

Welcome and Opening Remarks |

10:10 – 10:30

|

Title: When Does a Distributed Architecture Make Sense? Speaker: Aharon Brodutch, IonQ |

10:30 – 10:50

|

Title: Remote Entanglement of Superconducting Qubits Using Waveguide QED Speaker: Jeffrey Grover, MIT |

10:50 – 11:10

|

Title: Quantum Interconnect Based on Nanofiber Cavities Toward Distributed Fault-Tolerant Quantum Computing Speaker: Akihisa Goban, Nanofiber Quantum Technologies, Inc. (NanoQT) |

11:10 – 11:30

|

Title: Towards Fault-Tolerant Optical Interconnects for Neutral Atom Arrays Speaker: Josiah Sinclair, MIT |

Break (11:30 – 13:00) |

Session II |

Chair: Pooya Ronagh, 1QBit |

13:00 – 13:20

|

Title: How to Build a Quantum Supercomputer: Scaling from Hundreds to Millions of Qubits Speaker: John Martinis, Qolab and UC Santa Barbara |

13:20 – 13:40

|

Title: Photonic Interconnects in Trapped-Ion Quantum Computers Speaker: Sainath Motlakunta, IonQ |

13:40 – 14:00

|

Title: Using Flexible Connectivity to Improve Fault-Tolerance in Photonic Quantum Architectures Speaker: Mihir Pant, PsiQuantum |

14:00 – 14:30

|

Panel Discussion: Challenges of Realizing Quantum Interconnects Moderator: Pooya Ronagh, 1QBit Panellists: Aharon Brodutch, IonQ Erhan Saglamyurek, Lawrence Berkeley National Laboratory John Martinis, Qolab Yonatan Cohen, Quantum Machines |

Break (14:30 – 15:00) |

Session III |

Chair: Aharon Brodutch, IonQ |

15:00 – 15:20

|

Title: Entanglement Overheads of Fault-Tolerant Distributed Quantum Computing Speaker: Kaushik P. Seshadreesan, University of Pittsburgh |

15:20 – 15:40

|

Title: Costing Quantum Interconnects in Distributed Fault-Tolerant Compilation Speaker: Allyson Silva, 1QBit |

15:40 – 16:00

|

Title: Early Fault‑Tolerant Quantum Computing: Opportunities and Limits Speaker: Ming-Zhi Chung, QunaSys |

16:00 – 16:30

|

Panel Discussion: Compilation and Assembly for Distributed Fault-Tolerant Quantum Computing Architectures Moderator: Artur Scherer, 1QBit Panellists: Eneet Kaur, Cisco Katerina Gratsea, University of Wisconsin Masoud Mohseni, HPE Tommaso F. Demarie, Entropica Labs |

Speakers and Panellists

Aharon Brodutch

IonQ

Akihisa Goban

NanoQT

Allyson Silva

1QBit

Eneet Kaur

Cisco

Erhan Saglamyurek

Lawrence Berkeley National Laboratory

Jeffrey Grover

MIT

John Martinis

Qolab and UC Santa Barbara

Josiah Sinclair

MIT

Katerina Gratsea

University of Wisconsin

Kaushik P. Seshadreesan

University of Pittsburgh

Masoud Mohseni

HPE

Mihir Pant

PsiQuantum

Ming-Zhi Chung

QunaSys

Sainath Motlakunta

IonQ

Tommaso F. Demarie

Entropica Labs

Yonatan Cohen

Quantum Machines

Organizers

Aharon Brodutch

IonQ

Artur Scherer

1QBit

John Martinis

Qolab and UC Santa Barbara

Pooya Ronagh

1QBit

Contact

For any inquiries, please contact qce25-workshop@1qbit.com

Abstracts

When Does a Distributed Architecture Make Sense?

Speaker: Aharon Brodutch, IonQ

Time: Session I, 10:10 – 10:30

Abstract:

Modular distributed architectures provide a convenient path for scaling quantum computers. At the same time, moving quantum information across modules is slower and of lower fidelity than gates. In this talk, I will outline the main theoretical bottlenecks as well as the potential advantages of a distributed architecture.

Remote Entanglement of Superconducting Qubits Using Waveguide QED

Speaker: Jeffrey Grover, MIT

Time: Session I, 10:30 – 10:50

Abstract:

Future large-scale quantum computers will likely need quantum interconnects to realize, for example, quantum low-density parity-check codes or distributed quantum error correction. One paradigm for realizing such an interconnect with superconducting circuits is waveguide quantum electrodynamics (wQED), where a qubit is strongly coupled to the continuum of modes in a waveguide. In this talk, we present a demonstration of remote entanglement via chiral photon emission and absorption along a waveguide. Superconducting qubits couple to the waveguide at multiple, well-separated locations through modules that deterministically emit and absorb single microwave photons. Using this architecture, we demonstrate directional single-photon emission with 96% fidelity and single-photon absorption exceeding 60% efficiency. We then use partial emission and absorption to generate remote entanglement—a four-qubit W-state—between qubits in the emitter and absorber modules with 62% fidelity. These works, along with 3D integration, target modular and extensible quantum information processing mediated by quantum interconnects.

Quantum Interconnect Based on Nanofiber Cavities Toward Distributed Fault-Tolerant Quantum Computing

Speaker: Akihisa Goban, Nanofiber Quantum Technologies, Inc. (NanoQT)

Time: Session I, 10:50 – 11:10

Abstract:

Modular architectures of quantum processing units (QPU) offer a promising pathway to scalable fault-tolerant quantum computing by enabling multiple QPUs to operate synchronously through high-rate, high-fidelity photonic interconnects. We are developing a quantum interconnect platform based on nanofiber cavities integrated with tweezer-trapped ytterbium atoms. This system provides strong atom–photon coupling, a compact form factor, and seamless integration with fiber networks [1]. These features are essential for achieving high-rate and high-fidelity remote entanglement generation across distributed modules, which is a critical capability for scalable quantum networking.

In this talk, we present our progress on nanofiber-cavity-based interconnect hardware and its role in a distributed neutral-atom architecture for fault-tolerant quantum computing. We have recently proposed both active and passive modes of cavity-assisted quantum networking operation, each demonstrating remote entanglement generation at rates exceeding 100 kHz with fidelity above 0.999 [2,3]. We also outline how these physical-layer protocols are integrated into a logical surface-code-based architecture that incorporates shuttling-free syndrome extraction, pipelined resource-state factories, and potentially high-throughput intermodule gate teleportation [4].

[1] S. Sunami, S. Tamiya, R. Inoue, H. Yamasaki, and A. Goban, PRX Quantum 6, 010101 (2025).

[2] S. Kikura, R. Inoue, H. Yamasaki, A. Goban, and S. Sunami, arXiv:2502.14859 (2025).

[3] S. Kikura, K. Tanji, A. Goban, and S. Sunami, arXiv:2507.02333 (2025).

[4] S. Sunami, A. Goban, and H. Yamasaki, arXiv:2506.18979 (2025).

Towards Fault-Tolerant Optical Interconnects for Neutral Atom Arrays

Speaker: Josiah Sinclair, MIT

Time: Session I, 11:10 – 11:30

Abstract:

It has been recently shown that surface-code error-corrected qubits can be connected with noisy links without requiring distillation, better local gates, or space–time overheads [1]. Combining recent advances in atom arrays with these results, I will report progress towards a flexible experimental platform for modular quantum computing comprising a programmable Rydberg atom array interfaced with an optical cavity. In such a platform, fault-tolerant scaling via noisy photonic interconnects can be achieved with two-qubit gate and Bell pair error thresholds of 1% and 10%, respectively, as well as entanglement distribution fast enough to beat decoherence timescale.

[1] J. Ramette, J. Sinclair, N. P. Breuckmann, and V. Vuletić. “Fault-tolerant connection of error-corrected qubits with noisy links” (2023), arXiv:2302.01296 [quant-ph].

How to Build a Quantum Supercomputer: Scaling from Hundreds to Millions of Qubits

Speaker: John Martinis, Qolab and UC Santa Barbara

Time: Session II, 13:00 – 13:20

Abstract:

In the span of four decades, quantum computation has evolved from an intellectual curiosity to a potentially realizable technology. Today, small-scale demonstrations have become possible on hundreds of physical qubits and proof-of-principle error-correction on a single logical qubit. Nevertheless, the path toward a full-stack scalable technology is largely unknown. There are significant outstanding quantum hardware, fabrication, software architecture, and algorithmic challenges that are either unresolved or overlooked. Here, we show how the road to scaling could be paved by adopting existing semiconductor technology to build much higher-quality qubits and employing system engineering approaches.

Photonic Interconnects in Trapped-Ion Quantum Computers

Speaker: Sainath Motlakunta, IonQ

Time: Session II, 13:20 – 13:40

Abstract:

Trapped ions are a leading platform for quantum computing, offering high-fidelity local gates and a natural photonic interface for creating interconnects between multiple Quantum Processing Units (QPUs). While local computation and remote interconnect operations are both essential for a modular system, they often have competing resource requirements. To explore these challenges, this talk presents a use-case architecture that utilizes a multi-zone trap to physically separate a compute zone from a dedicated interconnect zone for remote entangling operations. In this scheme, remote entanglement is established via a heralded, probabilistic protocol where ion-photon entanglement is converted into ion-ion entanglement using a central Bell state measurement. I will then discuss some of the practical trade-offs that arise between the remote entanglement generation (REG) rates and the usable Bell pair fidelities.

Using Flexible Connectivity to Improve Fault-Tolerance in Photonic Quantum Architectures

Speaker: Mihir Pant, PsiQuantum

Time: Session II, 13:40 – 14:00

Abstract:

Photonic quantum computers offer qubits that are highly mobile and support flexible connectivity and operations. In this talk, we show how to exploit this flexibility to improve fault-tolerance while preserving modularity. We also discuss how other quantum platforms could leverage photonic interfaces to benefit from these strategies.

Entanglement Overheads of Fault-Tolerant Distributed Quantum Computingn

Speaker: Kaushik P. Seshadreesan, University of Pittsburgh

Time: Session III, 15:00 – 15:20

Abstract:

Realizing fault-tolerant distributed quantum computing (FT DQC) over a modular quantum computer requires careful evaluation of noise thresholds and entanglement overheads. Recent works have proposed various architectural frameworks for FT DQC, each aiming to progressively address the challenges of scaling quantum computing systems across spatially separated modules. Type 1 architectures are composed of modules, each containing a small number of memory and communication qubits, with one qubit per module becoming a data qubit in a quantum error correcting code. Type 2 architectures distribute a large error correcting code block across multiple modules, with most stabilizer measurements remaining local, except for a small subset at patch boundaries that are performed using nonlocal CNOT gates. Type 3 architectures assign code blocks to distinct modules and can perform fault tolerant operations such as transversal gates, lattice surgery, and teleportation to implement logical operations between code blocks. Using the planar surface code and toric code as representative examples, we analyze how the resource requirements, particularly the number of Bell pairs and the average number of generation attempts, scale with increasing code distance for the different architectural designs.

Costing Quantum Interconnects in Distributed Fault-Tolerant Compilation

Speaker: Allyson Silva, 1QBit

Time: Session III, 15:20 – 15:40

Abstract:

Distributing fault-tolerant quantum computation across a quantum network of multiple quantum processing units (QPU) will be a major technological milestone towards the realization of quantum utility. Quantum interconnects linking remote QPUs introduce significant space–time overheads, as the associated processes are typically slower and more error-prone than local intra-QPU operations. The primary motivation for this talk is to provide a realistic assessment of the associated impacts on the overall resource requirements for fault-tolerant execution of a quantum algorithm.

We use a modular 2D fault-tolerant architecture based on rotated surface codes and lattice surgeries between them as the framework for our investigation. Our simulations are based on lossy quantum state transfers at the physical level which are used to create logical Bell pairs via lattice surgery, which, in turn, are consumed as resources in implementing inter-QPU logical operations. We then demonstrate how the performance of the resulting inter-QPU operations impacts the accumulated logical error rates, the code distances required, and the total runtime and qubit count, using a quantum circuit for an example utility-scale application.

Early Fault‑Tolerant Quantum Computing: Opportunities and Limits

Speaker: Ming-Zhi Chung, QunaSys

Time: Session III, 15:40 – 16:00

Abstract:

Early fault-tolerant quantum computing (EFTQC) targets useful workloads on 10 k–100 k-qubit devices by reducing the most-costly elements of surface-code architectures. The STAR architecture exemplifies this approach: Clifford gates are fully protected, while non-Clifford operations use non-fault-tolerant analog rotations, removing the need for magic-state distillation and lowering qubit requirements. Using the quantum complex exponential least squares (QCELS) phase estimation algorithm, our resource estimates on chemistry and Hubbard benchmarks show up to a 10× reduction in physical qubits. The main challenge is the modest success rate of preparing high-fidelity rotation ancillas at large code distances, leading to the need for error mitigation that can stretch runtime orders of magnitudes beyond fully fault-tolerant baselines. Still, partial fault tolerance offers a promising path if hardware fidelity improves. Studying noise-robust EFTQC algorithms and shallow alternatives like quantum-selected configuration interaction (QSCI) may further advance partial fault tolerance toward practical advantage.

Contact

For any inquiries, please contact qce25-workshop@1qbit.com